# ТЕХНИЧЕСКИЕ НАУКИ

Научная статья УДК 621.391 DOI 10.35266/1999-7604-2023-3-6-16

# КОНФИГУРИРУЕМЫЙ СЛОЖНОФУНКЦИОНАЛЬНЫЙ БЛОК ОБРАБОТКИ ЦИФРОВЫХ СИГНАЛОВ

Алексей Викторович Башкиров 1, Сергей Анатольевич Гвозденко 2, Александр Александрович Пирогов<sup>3</sup>, Элеонора Викторовна Сёмка <sup>4⊠</sup>

1, 2, 3 Воронежский государственный технический университет, Воронеж, Россия

Аннотация. По результатам анализа типов и структур цифровых фильтров с конечной и бесконечной импульсной характеристикой и принципов их работы создана методика получения универсальной и устойчивой системы обработки сигналов с помощью конфигурируемого сложнофункционального блока их цифровой обработки на базе программируемых логических интегральных схем и фильтров разных типов, которая позволит создавать программно-аппаратные устройства под требуемый набор параметров обработки.

Ключевые слова: беспилотные авиационные системы, система цифровой обработки сигналов, цифровой фильтр, программируемая логическая интегральная схема

Финансирование: работа выполнена при финансовой поддержке Министерства науки и высшего образования Российской Федерации в рамках государственного задания (проект № FZGM-2023-0011).

**Для цитирования:** Башкиров А. В., Гвозденко С. А., Пирогов А. А., Сёмка Э. В. Конфигурируемый сложнофункциональный блок обработки цифровых сигналов // Вестник кибернетики. 2023. Т. 22, № 3. C. 6–16. DOI 10.35266/1999-7604-2023-3-6-16.

Original article

# CONFIGURABLE COMPLEX FUNCTION BLOCK FOR DIGITAL SIGNAL PROCESSING

Aleksey V. Bashkirov <sup>1</sup>, Sergey A. Gvozdenko <sup>2</sup>, Aleksandr A. Pirogov <sup>3</sup>, Eleonora V. Syomka <sup>4\infty</sup>

1, 2, 3 Voronezh State Technical University, Voronezh, Russia

and Y. A. Gagarin Air Force Academy, Voronezh, Russia

Abstract. According to the findings of an analysis of the types and structures of digital filters with finite- and infinite-impulse responses and the principles of their operation, a method for establishing a universal and stable system for signal processing has been developed using a configurable complex function block of digital signal processing based on the programming logical integral schemes and various types of filters in order to develop a software and hardware devices suitable for a set of processing parameters.

6

<sup>&</sup>lt;sup>4</sup> Военный учебно-научный центр Военно-воздушных сил «Военно-воздушная академия имени профессора Н. Е. Жуковского и Ю. А. Гагарина», Воронеж, Россия

<sup>&</sup>lt;sup>1</sup> fabi7@mail.ru, https://orcid.org/0000-0003-0939-722X

<sup>&</sup>lt;sup>2</sup> jgsar@mail.ru, https://orcid.org/0009-0003-7262-9748

<sup>3</sup> Pirogov.alx@gmail.com, https://orcid.org/0000-0002-5105-0505

<sup>&</sup>lt;sup>4</sup> semka elva@mail.ru <sup>⊠</sup>. https://orcid.org/0000-0002-0194-6979

<sup>&</sup>lt;sup>4</sup> Military Educational and Scientific Centre of the Air Force N. E. Zhukovsky

<sup>&</sup>lt;sup>1</sup> fabi7@mail.ru, https://orcid.org/0000-0003-0939-722X

<sup>2</sup> jgsar@mail.ru, https://orcid.org/0009-0003-7262-9748

<sup>&</sup>lt;sup>3</sup>Pirogov.alx@gmail.com, https://orcid.org/0000-0002-5105-0505

<sup>&</sup>lt;sup>4</sup> semka\_elya@mail.ru <sup>⊠</sup>, https://orcid.org/0000-0002-0194-6979

<sup>©</sup> Башкиров А. В., Гвозденко С. А.,

*Keywords:* unmanned aircraft systems, digital signals processing system, digital filter, programmed logical integral scheme

*Funding:* the study is supported by the Ministry of Science and Higher Education of the Russian Federation in the framework of a State task (project No. FZGM-2023-0011).

*For citation:* Bashkirov A. V., Gvozdenko S. A., Pirogov A. A., Syomka E. V. Configurable complex function block for digital signal processing. *Proceedings in Cybernetics*. 2023;22(3):6–16. DOI 10.35266/1999-7604-2023-3-6-16.

#### **ВВЕДЕНИЕ**

Цифровая фильтрация распознанных сигналов является обязательной процедурой при обнаружении и распознавании сообщений. Под фильтрацией понимают любое преобразование сигнала, при котором во входной последовательности обрабатываемых данных целенаправленно изменяются определенные соотношения между различными параметрами сигнала. Системы, которые выборочно изменяют форму сигнала, устраняют или уменьшают помехи, извлекают из сигналов определенную информацию и т. д., называются фильтрами. Соответственно, фильтры любого назначения являются частным случаем систем преобразования сигналов. Термин «цифровой фильтр» относится к аппаратной или программной реализации математического алгоритма, который определенным образом преобразует цифровой сигнал. Классификация цифровых фильтров обычно основывается на функциональных характеристиках алгоритмов цифровой фильтрации [1-3]. Цифровые фильтры могут иметь параметры, которые невозможно реализовать в аналоговых фильтрах, не требуют периодического контроля и калибровки, а один фильтр может обрабатывать несколько входных каналов или сигналов, при этом точность ограничивается только используемой разрядностью отсчетов [4]. Такие фильтры используются в цифровых авиационных системах и наиболее востребованы в комплексах самолетного типа, имеющих по сравнению с другими фильтрами низкую траекторную нестабильность. Более того, реализация блоков цифровой обработки сигналов на программируемых логических интегральных схемах (ПЛИС) значительно упростит аппаратные затраты и позволит максимально эффективно использовать эти возможности цифровых фильтров.

За последнее десятилетие индустрия беспилотных авиационных систем резко выросла.

Это связано с технологическими тенденциями и быстрым прогрессом в области управления, миниатюризации и компьютеризации, кульминацией которых являются безопасные, легкие, надежные и более экономичные беспилотные авиационные системы [5]. В связи с расширением применения беспилотных авиационных систем и увеличением поставленных задач — от стратегического и оперативного до тактического уровня, необходимо знание их потенциала и характеристик, а также представление о возможных проблемах с функциональностью.

С целью получения принципиально новых программно-аппаратных архитектур были выполнены:

- 1. Анализ существующих на сегодняшний день методик преобразования сигналов.

- 2. Изучены способы реализации известных архитектур цифровых фильтров.

- 3. Сформированы требования к итерационно-вычислительному блоку, применимому в большинстве известных архитектур цифровых фильтров.

- 4. Сформированы требования к системе вычислительных блоков для их совместной работы в системе обработки сигналов.

- 5. Проделана корректировка требований, предъявляемых к блоку, учитывая проблематику групповой работы итерационно-вычислительных блоков в составе системы обработки сигналов.

- 6. Разработаны архитектуры итерационновычислительного блока и их интеграция в систему.

Цель – проведение изысканий в области цифровой обработки сигналов для получения принципиально новых программно-аппаратных архитектур, разработка модели RTL (register transfer level, уровень передачи регистров) сложнофункционального блока (СФ-блока) системы цифровой обработки сигналов, ее верификация как на логическом, так и на физическом уровне.

#### МАТЕРИАЛЫ И МЕТОДЫ

# 1. Анализ современных систем цифровой обработки сигналов беспилотных летательных аппаратов

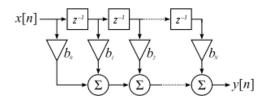

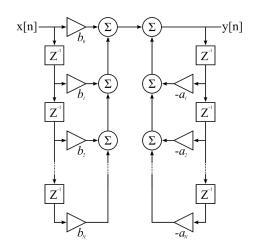

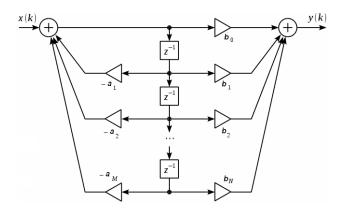

Особенностью цифровых фильтров с конечной импульсной характеристикой (КИХ) является их ограничение по времени. Фильтры с бесконечной импульсной характеристикой (БИХ) отличаются наличием обратной связи. На рис. 1-2 представлены схемы указанных архитектур. В КИХ-фильтрах для вычисления значений выходных сигналов y(n) используются текущие значения входных сигналов x(n), которые определяются мгно-

венным значением и суммой  $\sum$  предыдущих отчетов линии  $z^{-1}$  с учетом заданных коэффициентов фильтра  $b_n$ . Преимуществом КИХфильтров является их высокая устойчивость и возможность формирования требуемой фазовой и амплитудно-частотной характеристики. Но КИХ-фильтры в значительной мере требовательны к ресурсам системы обработки сигналов, а также обладают достаточно высокими показателями задержки [6–8]. БИХфильтры отличаются более низкой задержкой и простотой расчета, но наличие обратной связи (учет коэффициентов  $a^n$ ) может привести к снижению устойчивости при работе.

Рис. 1. Фильтр с конечной импульсной характеристикой Примечание: составлено авторами по [6].

Рассмотрев ключевые особенности различных типов фильтров, авторы выявили, что для построения универсальной конфигурируемой системы цифровой обработки сигналов необ-

ходимо использовать программно-аппаратные модели фильтров для корректировки их параметров в процессе работы с учетом их архитектурных преимуществ и недостатков.

Рис. 2. Фильтр с бесконечной импульсной характеристикой Примечание: составлено авторами по [6].

# 2. Разработка программируемого СФ-блока цифровой обработки сигналов на базе программируемых логических интегральных схем

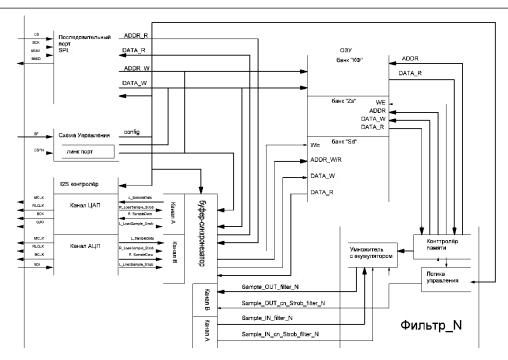

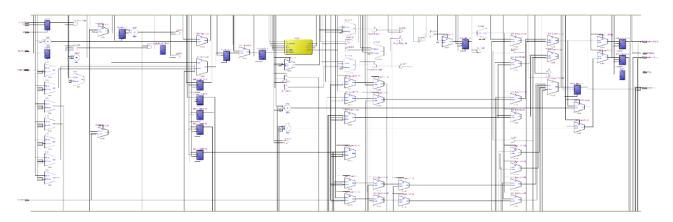

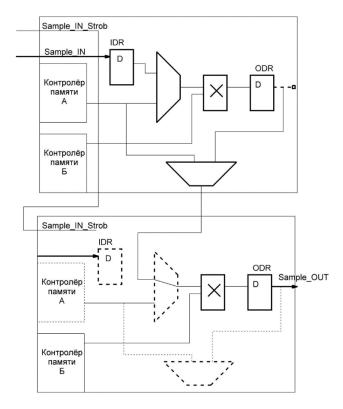

СФ-блок цифровой обработки сигналов обеспечивает работу цифрового фильтра с ко-

нечной импульсной характеристикой в разных режимах путем программного задания его параметров (рис. 3). В модели предусмотрен ряд периферийных блоков, обеспечивающих работу фильтра в тестовом режиме [9].

<sup>©</sup> Башкиров А. В., Гвозденко С. А., Пирогов А. А., Сёмка Э. В., 2023

**Рис. 3. Общая функциональная схема программно-аппаратного сложнофункционального блока** *Примечание:* составлено авторами на основании данных, полученных в исследовании.

Программно-аппаратный модуль позволяет обеспечить обработку сигналов, содержит ряд блоков, которые рассмотрим ниже.

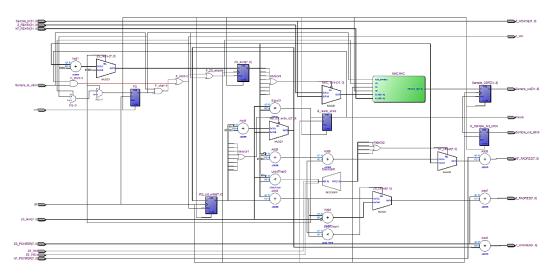

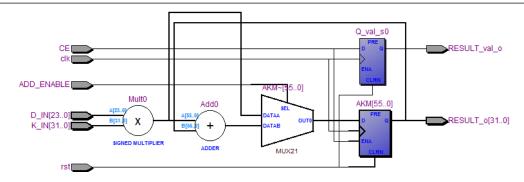

Вычислительный блок ядра фильтра (рис. 4) предназначен для производства итерационных операций над данными, получаемыми с входа из входного регистра данных блока, выходного регистра данных блока, а также

данных, получаемых от ведущего блока быстрого переноса при совместной работе нескольких блоков. Модуль включает в свою структуру два контроллера памяти, систему управления блока, вычислителей смещений, вычислительный блок умножений и вычислительное устройство.

Рис. 4. Схема ядра фильтра

Примечание: составлено авторами на основании данных, полученных в исследовании.

Блок управления предназначен для контроля каскадами фильтра, выдачи сигналов управления чтения и записи данных в линию

сдвига. Блок умножителя осуществляет умножение данных с фиксированной точкой и их накопление (рис. 5).

<sup>©</sup> Башкиров А. В., Гвозденко С. А., Пирогов А. А., Сёмка Э. В., 2023

Рис. 5. Схема умножителя

Примечание: составлено авторами на основании данных, полученных в исследовании.

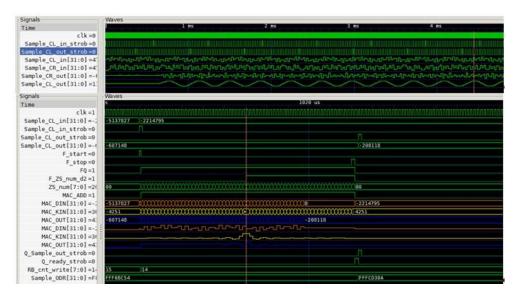

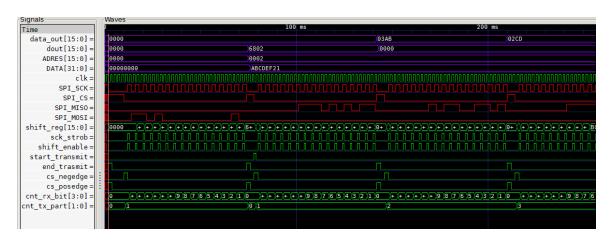

Была проведена верификация полученной модели, построены временные диаграммы работы модуля, представленные на рис. 6, кото-

рые подтверждают адекватность полученных моделей и соответствие результатов моделирования расчетным параметрам [10].

Рис. 6. Временная диаграмма работы фильтра

Примечание: составлено авторами на основании данных, полученных в исследовании.

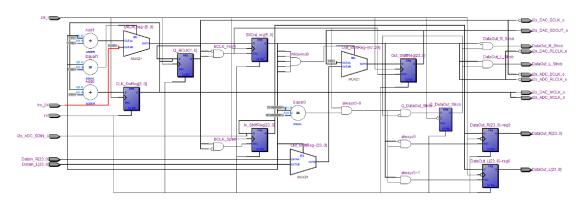

На рис. 7 представлена схема периферийного блока  $I^2S$  для передачи сигналов синхро-

низации данных, временная диаграмма блока представлена на рис. 8.

Рис. 7. Схема блока I<sup>2</sup>S

<sup>©</sup> Башкиров А. В., Гвозденко С. А., Пирогов А. А., Сёмка Э. В., 2023

Рис. 8. Временная диаграмма работы блока I<sup>2</sup>S

Примечание: составлено авторами на основании данных, полученных в исследовании.

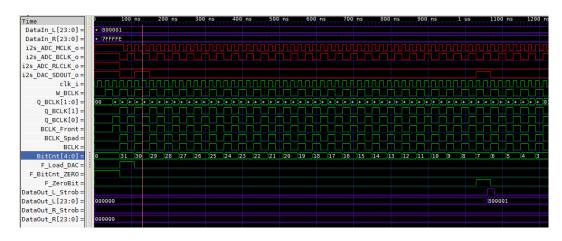

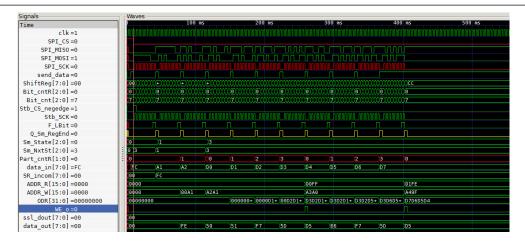

Блок SPI (рис. 9) предназначен для получения доступа устройством управления к памяти и регистрам управления. На рис. 10 показана

временная диаграмма работы блока SPI в режиме «C-D8», на рис. 11 — временная диаграмма работы блока SPI в режиме «serial».

**Рис. 9. Схема блока SPI** Примечание: составлено авторами на основании данных, полученных в исследовании.

Рис. 10. Временная диаграмма работы блока SPI в режиме «C-D8»

<sup>©</sup> Башкиров А. В., Гвозденко С. А., Пирогов А. А., Сёмка Э. В., 2023

Рис. 11. Временная диаграмма работы блока SPI в режиме «serial» *Примечание:* составлено авторами на основании данных, полученных в исследовании.

## РЕЗУЛЬТАТЫ И ИХ ОБСУЖДЕНИЕ

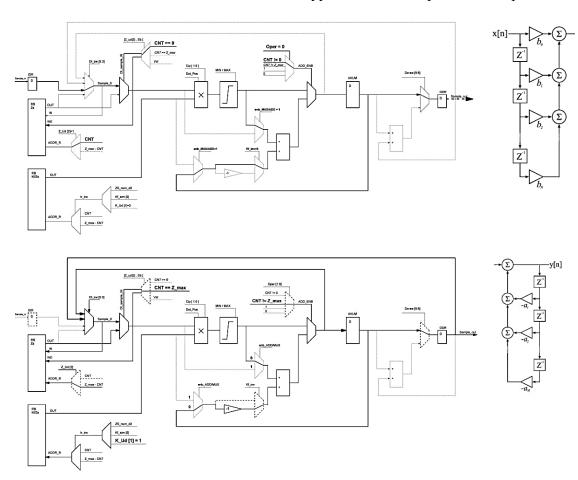

Разработана модель цифрового фильтра, способного на программном уровне перестраивать свою конфигурацию для обеспечения параллельной работы двух и более вычислительных блоков, которая позволяет декомпозировать БИХ-фильтр. На рис. 12 представлены конфигурации вычислительных блоков для обработки разных ветвей БИХ-фильтра. Данные ветви могут быть обработаны одним программно-аппаратным блоком с реконфигурацией или в параллельном режиме.

Рис. 12. Конфигурации вычислительных блоков для обработки разных ветвей фильтра с бесконечной импульсной характеристикой

<sup>©</sup> Башкиров А. В., Гвозденко С. А.,

Данный программно-аппаратный модуль позволяет реализовать работу согласно архи-

тектуре БИХ-фильтра с использованием одной линии задержки (рис. 13).

Рис. 13. Архитектура фильтра с бесконечной импульсной характеристикой с одной линией задержки *Примечание:* составлено авторами по [6].

Далее дадим разъяснение предложенной и реализованной методики декомпозиции цифровой системы обработки сигналов. Так как блоков несколько, а линия задержки одна на две ветви, возникает проблема доступа к одной и той же области памяти для двух ветвей и решение ее двумя способами, один

из которых представлен на рис. 14. Необходимо предоставить один канал к памяти для блоков и использовать вычислитель адреса ведущего блока, а данные, поступающие в ведущий блок, транслировать в ведомый, введя линию переноса.

Рис. 14. Схема взаимодействия двух вычислительных блоков при вычислении с одной линией задержки фильтра

<sup>©</sup> Башкиров А. В., Гвозденко С. А., Пирогов А. А., Сёмка Э. В., 2023

Данный способ позволяет использовать DMA (direct memory access, прямой доступ к памяти) для использования внешней памяти. DMA – это режим обмена данными между функциональными узлами без участия в работе центрального процессора, что в целом увеличивает скорость обмена информацией и повышает эффективность работы всей системы. При количестве итераций, превышающих размерность буфера, существует возможность работы с DMA, область буфера разбивается на участки, когда счетчик итераций выходит за диапазон участка памяти. Для работы DMA требуется разбить пространство внутренней кэш-памяти на разделы и ввести счетчик раздела, при переполнении которого поступает команда для запуска канала DMA. По команде DMA начинает перенос данных раздела кэш-памяти во внешнюю память. Когда DMA закончит работу, то происходит сброс флага занятости страницы. Если вычислительный блок перешел к началу страницы памяти, а флаг при этом не сброшен, то блок выдает прерывание в системе управления, а при сбросе флага продолжит свою работу [11].

Есть другой способ: поскольку кэш-память имеет два независимых информационных порта, то можно дать вычислителям блоков, обрабатывающих разные ветви фильтра, разные каналы памяти, обеспечивающие доступ к единому адресному пространству памяти [12], тем самым исключив доступ к страницам памяти для DMA. Это не позволяет при помощи DMA расширить внутреннюю память вычислительных блоков за счет внешнего ресурса памяти. Данный способ актуален для работы, где нет необходимости иметь доступ к внешней памяти для вычислений большого количества итераций.

В разработанной модели были учтены оба способа, что позволяет сконфигурировать более универсальную и устойчивую систему цифровой обработки сигналов. Разработанная система обработки сигналов на основе полученных в ходе исследования сложно концентрируемых блоков была реализована и прошла физическую верификацию на базе отладочной платы Basys 2 с использованием ПЛИС Xilinx Spartan 3E [13]. Отладочная плата в своем составе имеет постоянное запоминающее устройство (ПЗУ), необходимое

для записи и хранения прошивки программируемой пользователем вентильной матрицы. При подаче питания на плату на основе записанной прошивки в ПЗУ происходит конфигурирование вентильной матрицы, в результате чего получаем готовое к работе запрограммированное устройство. Отладочная плата содержит ряд элементов управления и индикации (переключатели, тактовые кнопки, светодиодные индикаторы, семисегментный индикатор), есть возможность использования дополнительных внешних устройств за счет их подключения к универсальным программируемым портам ввода/вывода. При проведении верификации использованы внешние модули аналогово-цифрового преобразователя и цифро-аналогового преобразователя для подачи и приема обработанного сигнала. В качестве устройства управления использован микроконтроллер, который при включении и по прерываниям от испытываемой системы производил смену конфигураций СФ-блоков и загружал коэффициенты фильтров во внутреннюю память. Реконфигурируемое устройство тестировалось в режимах работы фильтра нижних и верхних частот, полосового фильтра. Работа тестовой системы подтвердила результаты моделирования, из чего можно сделать вывод, что полученная модель является полной и работоспособной.

# **ЗАКЛЮЧЕНИЕ**

В ходе проведенного научного исследования был произведен анализ литературных источников, типов цифровых фильтров и принципов их работы. Рассмотрев ключевые особенности различных типов фильтров, авторы выявили, что для построения универсальной конфигурируемой системы цифровой обработки сигналов необходимо использовать программно-аппаратные модели фильтров для корректировки их параметров в процессе работы с учетом их архитектурных преимуществ и недостатков.

Разработана методика декомпозиции системы цифровой обработки сигналов, внутрисистемного взаимодействия моделей элементов системы цифровой обработки сигналов. В результате работы и моделирования получены модели конфигурируемого фильтра, проведена его верификация.

В целях верификации и подтверждения адекватности разработанной в ходе исследования методики была создана модель СФ-блок цифровой обработки сигналов. Данная модель реализована и прошла физическую верификацию на базе отладочной платы с использованием программируемых логических интегральных схем. В качестве управляющего устройства был использован микроконтроллер,

который загружает программу управления и таблицу коэффициентов фильтра. Реконфигурируемое устройство тестировалось в режимах работы фильтра нижних и верхних частот, полосового фильтра. Работа тестовой системы подтвердила результаты моделирования, из чего можно сделать вывод, что полученная модель является полной и работоспособной.

#### Список источников

- 1. Васюков В. Н. Цифровая обработка сигналов и сигнальные процессоры в системах подвижной радиосвязи. Новосибирск: Изд-во НГТУ, 2006. 292 с.

- 2. Лэм Г. Аналоговые и цифровые фильтры / пер. с англ. М. : Мир, 1982. 592 с.

- 3. Екимов Е. Н., Платоненков С. В. Цифровые фильтры: виды и реализация // Актуальные вопросы инновационного развития Арктического региона РФ: сб. материалов Всерос. науч.-практич. конф., 18–20 ноября 2019 г., г. Северодвинск. Архангельск: ИД САФУ, 2020. С. 202–206.

- Гулевич С. П., Александровский Б. В., Веселов Ю. Г. Обоснование основных требований к характеристикам движения беспилотных летательных аппаратов двойного назначения // Проблемы безопасности полетов. 2008. № 8. С. 25–39.

- 5. Управление и наведение беспилотных маневренных летательных аппаратов на основе современных информационных технологий / под ред. М. Н. Красильщикова и Г. Г. Себрякова. М.: ФИЗМАТЛИТ, 2003. 280 с.

- 6. Айфичер Э. С., Джервис Б. У. Цифровая обработка сигналов: практический подход. 2-е изд. / пер. с англ. М.: Вильямс, 2004. 992 с.

- 7. Коберниченко В. Г. Основы цифровой обработки сигналов. Екатеринбург : Изд-во Урал. федер. ун-та, 2018. 150 с.

- Кестер У. Проектирование систем цифровой и смешанной обработки сигналов / пер. с англ. под ред. А. А. Власенко. М.: Техносфера, 2010. 328 с.

- 9. Пирогов А. А., Пирогова Ю. А., Гвозденко С. А. и др. Разработка реконфигурируемых устройств на основе программируемых логических интегральных схем // Вестник Воронежского государственного технического университета. 2020. Т. 16, № 6. С. 90–97.

- Pirogov A. A., Glotov V. V., Pirogova Yu. A. et al. The development of dynamically reconfigurable devices of digital signal processing based on field programmable gate array. In: AIP Conf Proc. Proceedings of the VII International Young Researchers Conference "Physics, Technology, Innovations (PTI-2020)", May 18–22, 2020, Yekaterinburg. Vol. 2313. p. 070022.

- 11. Богословский А. В., Разиньков С. Н., Сёмка Э. В. и др. Применение программируемых логических

#### References

- 1. Vasyukov V. N. Tsifrovaia obrabotka signalov i signalnye protsessory v sistemakh podvizhnoi radiosviazi. Novosibirsk: Publishing House of NSTU; 2006. 292 p. (In Russian).

- 2. Lam H. Analog and digital filters: Design and realization. Moscow: Mir; 1982. 592 p. (In Russian).

- 3. Ekimov E. N., Platonenkov S. V. Tsifrovye filtry: vidy i realizatsiia. In: *Proceedings of the All-Russian Research-to-Practice Conference "Aktualnye voprosy innovatsionnogo razvitiia Arkticheskogo regiona RF"*, November 18–20, 2019, Severodvinsk. Arkhangelsk: Publishing House of NArFU; 2020. p. 202–206. (In Russian).

- Gulevich S. P., Aleksandrovsky B. V., Veselov Yu. G. Obosnovanie osnovnykh trebovanii k kharakteristikam dvizheniia bespilotnykh letatelnykh apparatov dvoinogo naznacheniia. *Problemy bezopasnosti* poletov. 2008;(8):25–39. (In Russian).

- Krasilshchikov M. N., Sebryakov G. G., editors. Upravlenie i navedenie bespilotnykh manevrennykh letatelnykh apparatov na osnove sovremennykh informatsionnykh tekhnologii. Moscow: FIZMATLIT; 2003. 280 p. (In Russian).

- 6. Ifeachor E. C., Jervis B. W. Digital signal processing: A practical approach. 2nd ed. Moscow: Williams; 2004. 992 p. (In Russian).

- 7. Kobernichenko V. G. Osnovy tsifrovoi obrabotki signalov. Yekaterinburg: Publishing House of UrFU; 2018. 150 p. (In Russian).

- 8. Kester W. Mixed-signal and DSP design techniques. Vlasenko A. A., editor. Moscow: Tekhnosfera; 2010. 328 p. (In Russian).

- 9. Pirogov A. A., Pirogova Yu. A., Gvozdenko S. A. et al. Development of reconfigurable devices based on programmable logic integrated circuits. *The Bulletin of Voronezh State Technical University*. 2020;16(6):90–97. (In Russian).

- Pirogov A. A., Glotov V. V., Pirogova Yu. A. et al. The development of dynamically reconfigurable devices of digital signal processing based on field programmable gate array. In: AIP Conf Proc. Proceedings of the VII International Young Researchers Conference "Physics, Technology, Innovations (PTI-2020)", May 18–22, 2020, Yekaterinburg. Vol. 2313. p. 070022.

- 11. Bogoslovsky A. V., Razinkov S. N., Syomka E. V. et al. Applying field programmable gate arrays in systems

- интегральных схем в системах многоканальной цифровой обработки сигналов спутниковой навигации // Вестник кибернетики. 2023. Т. 22, N 2. С. 13–20.

- 12. Новиков Ю. В., Скоробогатов П. К. Основы микропроцессорной техники. М. : НОЦ «ИНТУИТ», 2009. 357 с.

- 13. Нечаев Е. Е. К вопросу построения интегрированных навигационных систем на базе ПЛИС // Научный вестник МГТУ ГА. 2008. № 136. С. 85–95.

### Информация об авторах

- **А. В. Башкиров** доктор технических наук, доцент, проректор по науке и инновациям.

- С. А. Гвозденко младший научный сотрудник.

- А. А. Пирогов кандидат технических наук, доцент.

- **Э. В. Сёмка** кандидат физико-математических наук, доцент.

- of multichannel digital processing of satellite navigation signals. *Proceedings in Cybernetics*. 2023;22(2):13–20. (In Russian).

- 12. Novikov Yu. V., Skorobogatov P. K. Osnovy mikroprotsessornoi tekhniki. Moscow: NOTs "INTUIT"; 2009. 357 p. (In Russian).

- 13. Nechaev E. E. On problem of integrated navigation systems on the basis of FPGA. *Civil Aviation High Technologies*. 2008;(136):85–95. (In Russian).

#### Information about the authors

- **A. V. Bashkirov** Doctor of Sciences (Engineering), Docent, Vice-Rector in Science and Innovations.

- S. A. Gvozdenko Junior Researcher.

- **A. A. Pirogov** Candidate of Sciences (Engineering), Docent.

- **E. V. Syomka** Candidate of Sciences (Physics and Mathematics), Docent.